AI Won’t Replace Semiconductor Engineers. It’s Creating Demand for a New Kind.

Every few months, a new headline declares that AI is about to make engineers obsolete. In the semiconductor industry specifically, the question keeps surfacing: if Synopsys can generate RTL from a text prompt, do you still need a 20-year veteran to write it?

The short answer is yes. Emphatically. But the longer answer is more instructive. AI is changing the work that principal-level semiconductor engineers do. It is not eliminating the need for them. In several disciplines, it is accelerating demand.

Here's what is actually happening.

What AI Is Actually Doing in Chip Design

The EDA vendors are not being subtle about this. Synopsys launched its AI Copilot in 2023 and has continued expanding it. As of September 2025, it can generate RTL code, SystemVerilog Assertions (SVAs), and UVM testbenches from natural language inputs; accelerating certain workflows, in Synopsys’ own words, “from days to hours, and hours to minutes.” Siemens EDA unveiled AI-powered tools at DAC 2025 built on NVIDIA NIM microservices, targeting layout optimization, simulation, and verification. Cadence has its own AI-driven tooling in production.

These are real productivity gains. In RTL design and verification, where engineers often spend weeks writing repetitive testbench infrastructure, AI is a legitimate accelerant. For DFT teams, no-code interfaces are beginning to allow power-control, clock, and scan insertion sequences to be configured from a GUI rather than scripted entirely in Tcl.

This is where the “AI replaces engineers” narrative starts and stops.

What AI Cannot Do, and Why It Matters for Sign-Off

Synopsys’ own numbers are telling. Their AI Copilot’s assertion assistant achieves 80% syntax accuracy and 70% functional accuracy on SVAs. That means roughly 1-in-4 generated assertions has a functional problem that requires an engineer to catch and fix. For verification - where the entire point is to prove design correctness - that gap cannot be filled by another AI pass. It requires a Verification Architect who understands design intent deeply enough to know what “wrong” looks like.

Semiconductor Engineering puts it directly: “AI can help teams reach formal sign-off faster, but it cannot replace the guarantees that formal verification provides.” The same principle holds across disciplines:

- Physical Design Engineers — An AI-assisted place-and-route run still produces a layout that must be signed off for IR drop, electromigration, STA closure, and DRC. Those calls require someone who has seen parasitics cause silicon failures. The reference tools - Synopsys PrimeTime, Siemens Calibre - still require an engineer to interpret the results and make the call.

- DFT Engineers — ATPG tools generate test patterns. Deciding which scan architecture is appropriate for a multi-die SoC with mixed power domains, or what MBIST strategy fits a specific memory topology, is a judgment call. Synopsys DFT Compiler and Siemens Tessent automate execution; they don’t architect the strategy. That belongs to the DFT Architect.

- Verification Engineers — AI can scaffold UVM environments and generate directed tests faster than any engineer. But closing coverage at the SoC level - especially on protocols like DDR5 or PCIe, or safety-critical paths requiring ISO 26262 compliance - requires a principal-level Verification Architect. The plan and judgment behind it belong to the engineer.

- Embedded Firmware Engineers — Hardware-software bring-up on a new SoC does not follow a script. When a peripheral doesn’t enumerate on first spin or an interrupt storm locks the RTOS at 3 AM, you need deep embedded systems experience. No model has scar tissue from silicon.

Semiconductor Engineering’s analysis framed it precisely: “You cannot parallelize judgment. AI-powered design needs the ingredient traditional tooling cannot invent: the tacit knowledge that senior engineers apply when the data is ambiguous.”

The Talent Gap Is Getting Wider, Not Narrower

Here is the part that undercuts the replacement narrative entirely: the industry does not have too many engineers. It has a structural shortage that is worsening.

Deloitte projects that the global semiconductor industry will need more than one million additional skilled workers by 2030 - roughly 100,000 per year, every year, through the end of the decade. The Semiconductor Industry Association estimates a U.S.-specific shortfall of 67,000 workers by 2030. Against that backdrop, there are fewer than 100,000 graduate students enrolled annually in electrical engineering and computer science across the entire United States.

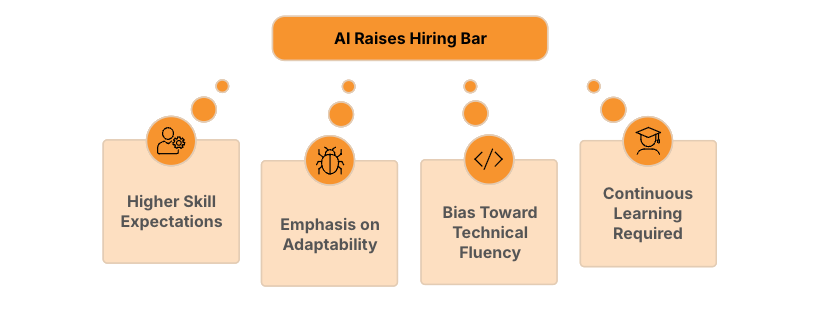

Synopsys has acknowledged this directly: its AI tooling is positioned to “address productivity bottlenecks amid a workforce shortage,” not to reduce headcount. When there are not enough engineers to begin with, making each engineer more productive raises the baseline expectation of what one engineer delivers, which means the bar for who gets hired goes up, not down.

The New Profile: What an AI-Enabled Semiconductor Engineer Looks Like

The engineers in highest demand right now are not being replaced by AI. They are the ones who know their discipline deeply enough to use AI tools effectively, and to recognize when the output is wrong.

RTL Design Engineers

AI-generated SystemVerilog is accelerating first-pass RTL coding. Synopsys reports productivity gains that compress workflows from days to hours. But engineers who can review AI-generated RTL for clock domain crossing (CDC) hazards, reset strategy problems, and synthesis gotchas - and who understand the microarchitecture well enough to prompt the tool correctly - are dramatically more productive than those who cannot. The tool amplifies skill. It also exposes its absence.

Verification Engineers

AI can scaffold UVM environments faster than any engineer writing from scratch. But the verification plan - what needs to be covered, what the failure modes are, how to close coverage on a complex protocol like PCIe Gen5 or DDR5 - still requires a principal-level Verification Architect. The engineer’s role is shifting from writing testbench boilerplate to owning coverage strategy and reviewing AI output.

DFT Engineers

ATPG and MBIST pattern generation are increasingly automated through tools like Synopsys TetraMAX and Siemens Tessent. But the structural DFT architecture - scan chain topology, compression ratios via DFTMAX or TestKompress, test time budgeting, how test logic interacts with power management across voltage domains - is not something a model decides. That is a design choice with yield and per-unit cost implications, and it belongs to the DFT Architect.

Physical Design Engineers

AI-driven placement and routing is improving quality of results (QoR) in ways that previously required dozens of manual iterations.

Synopsys reports up to 3x productivity gains and up to 20% better QoR in AI-assisted flows with tools like IC Compiler II and Fusion Compiler. But PD engineers are still the ones reading the PrimeTime timing reports, triaging DRC violations in Calibre, and making the tapeout calls.

What This Means If You’re Hiring

The shift to AI-augmented design flows is real, and hiring managers at semiconductor companies are starting to weight it in technical screens. But the core hiring bar has not dropped. The most valuable engineers are the ones who operate at a higher level of abstraction and can direct the AI tools rather than work around them.

A candidate who has used Synopsys.ai Copilot or worked in an AI-assisted verification flow has a genuine edge. But a candidate who understands why the AI-generated SVA is functionally wrong at line 47 is the one you actually want on your program.

The shortage of engineers who have both domain depth and AI fluency is real and growing. That combination is not coming out of university programs at scale. It is coming from experienced engineers who have deliberately integrated these tools into their practice.

What This Means If You’re an Engineer

Your domain expertise is not becoming less valuable. It is becoming the prerequisite for using AI tools correctly. An AI that generates a UVM testbench without understanding the protocol it is supposed to verify is just fast noise. The engineer who knows the protocol is what makes the tool useful.

The engineers who will have the most leverage in the next five years are the ones who treat these tools the way experienced engineers have always treated new EDA releases: with healthy skepticism, a sharp eye for the delta between what the tool claimed and what it actually delivered, and the experience to know the difference.

The industry needs more of you, not fewer.

Deloitte’s numbers are not wrong. The demand is structural and it is not going away.

The Bottom Line

AI is not a headcount reduction strategy for semiconductor engineering teams. It is a force multiplier for engineers who are already good and a growing dividing line between the ones who adapt and the ones who do not.

The demand for principal-level DFT Engineers, Verification Architects, RTL Design Engineers, Physical Design Engineers, and Embedded Firmware Engineers is not softening because of AI. It is rising. The profile of who gets those roles is shifting toward engineers who can operate AI-assisted toolchains without being fooled by them.

That is a different job than replacing engineers. It is a more demanding one.

If you're looking to find domain experts who are AI-enabled, reach out to us and we'll find you the right engineer for your problem. If you're looking for a new role, click here.

Frequent Asked Questions

FAQ: AI and Enginee

Will AI replace semiconductor engineers?

No. AI EDA tools like Synopsys.ai Copilot are accelerating specific tasks - RTL generation, testbench scaffolding, SVA writing, and route optimization - but they require experienced engineers to review output, correct errors, and make sign-off decisions.

Deloitte projects the global semiconductor industry will need more than one million additional skilled workers by 2030. AI is addressing a productivity shortage, not creating a headcount surplus.

Which semiconductor engineering disciplines are most affected by AI?

RTL design and verification are seeing the most immediate impact, with AI tools generating SystemVerilog, SVAs, and UVM testbenches. Physical design and DFT are seeing AI-assisted optimization in place-and-route flows (ICC2, Innovus) and ATPG. Embedded firmware engineering is less directly affected by EDA AI tools, as bring-up and hardware-software integration remain highly context-dependent and hardware-specific.

How should hiring managers adjust requirements for AI-era chip engineers?

The bar for domain expertise has not lowered - it has become the minimum required to use AI tools correctly. Look for candidates who have used AI-assisted design tools in production and can speak critically about output quality. Candidates who can describe where the tool helped and where it fell short (and why) are demonstrably more valuable than those who have not engaged with these tools at all.

What skills should a semiconductor engineer develop to stay relevant as AI tools improve?

Domain depth first. An engineer who understands functional coverage strategy, DFT architecture, or STA constraints can use AI tools effectively and catch errors in AI-generated output. AI fluency without domain expertise produces fast, wrong answers. Engineers who combine deep discipline knowledge with working familiarity with AI-assisted EDA flows will be the most sought-after.